حل تشریحی سوالات الکترونیک دیجیتال - کنکور ارشد مهندسی کامپیوتر 1401

منوی آزمون (درس ها)

سوالات الکترونیک دیجیتال

6 سوالطراحی یک مدار CMOS ایستا برای یک میکروکنترلر قرار است با فرکانس 500 مگاهرتز کارکند. خروجی یک وارونگر نوعی در این طراحی با نرخ 0/1 فرکانس کلاک تغییر میکند و طبق مشخصات، مصرف توان نباید بیش از 10 میکرووات باشد. بیشینه مقدار خازن بار وارونگر چند فمتوفاراد باشد تا این محدودیت براورده شود؟ (VDD= 2V)

(از مصرف توان ایستا صرف نظر کنید)

10

50

100

500

تابع F با جدول درستی زیر را در نظر بگیرید. برای پیاده سازی این تابع با استفاده از مدار CMOS ایستا حداقل به چند ترانزیستور نیاز است؟ (فرض کنید فقط خود ورودی ها در دسترس هستند.)

12

10

8

6

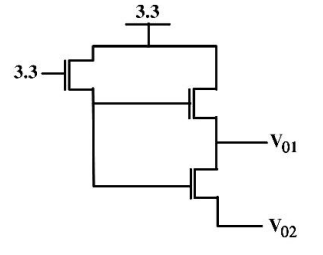

در مدار زیر، ولتاژ فقط و به ترتیب، از راست به چپ، چقدر است؟ (ولتاژ استانه ترانزیستورها 0/5 ولت است)

2/3 , 2/3

2/8 , 3/3

2/8 , 2/8

2/3 , 2/8

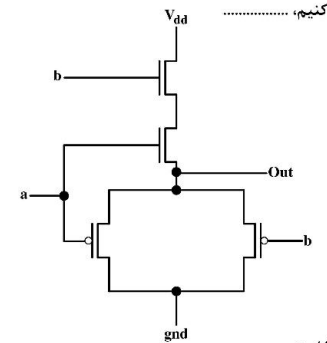

درصورتی که برای پیاده سازی گیت AND ، از مدار مقابل استفاده

این مدار منطق AND را پیاده سازی نمیکند

مدار کار میکند، ولی تاخیر ان بیشتر از مدار AND رایج CMOS است.

مدار کار میکند، ولی ولتاژهای خروجی برای منطق صفر و یک کامل نیستند

مدار کار میکند، ولی توان مصرفی ان بیشتر از مدار AND رایج CMOS است.

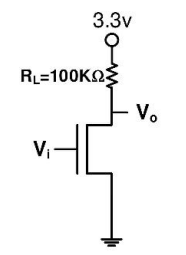

در مدار شکل زیر، مقدار ترانزیستور NMOS برابر کدام مورد باشد تا حاشیه نویز حالت LOW برابر 0/5 ولت باشد؟ ( فرض کنید مقدار 0/5v , 0/5 v و مقدار ='K است)

4

2

کدام مورد برای دروازه های منطقی در فناوری CMOS ایستا، درست است؟

پدیده مدولاسیون طول کانال باعث کاهش جریان درین- سورس در زمان روشن بودن ترانزیستورها میشود.

توان مصرفی پویا در این فناوری با خازن بار نسبت مستقیم و با فرکانس کلاک نسبت عکس دارد.

عامل اصلی محدود کننده بار خروجی (fanout) تاخیر مطلوب طراح است

افزایش ولتاژ تغذیه (Vdd) باعث افزایش تاخیر دروازه میشود